InSEQt Handbuch: Unterschied zwischen den Versionen

Tomcat (Diskussion | Beiträge) |

|||

| (10 dazwischenliegende Versionen von 2 Benutzern werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

== Pre-Patchings == | == Übersicht == | ||

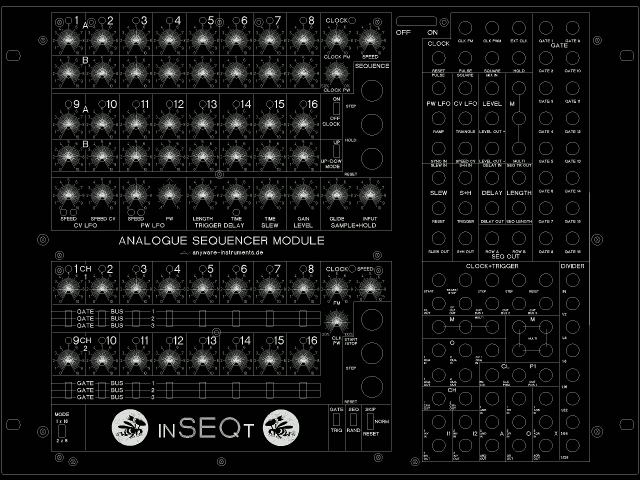

[[File:Inseqt_front_klein.png|link=File:Inseqt_front.png]] | |||

== Ein-/Ausgänge mit Pre-Patchings == | |||

'''Oberer Teil:''' | '''Oberer Teil:''' | ||

{| class="wikitable" | {| class="wikitable" | ||

|- class="hintergrundfarbe5" | |- class="hintergrundfarbe5" | ||

! Buchse !! Art !! | ! Modul !! Buchse !! Art !! Pre-Patch !! Beschreibung | ||

|- | |- | ||

| | | Clock || CLK [[FM]] || IN || RAMP || Clock Frequency | ||

|- | |- | ||

| | | Clock || CLK [[PWM]] || IN || || Länge des Gates | ||

|- | |- | ||

| | | Clock || EXT CLK || IN || || Externe Clock | ||

|- | |- | ||

| | | Clock || RESET || IN || || Zurück auf Gate 1 | ||

|- | |- | ||

| | | Clock || PULSE || OUT || || Gate als Rechteck | ||

|- | |- | ||

|SQUARE || OUT || | | Clock || SQUARE || OUT || || Gate als 50% Rechteck | ||

|- | |- | ||

| | | Clock || HOLD || IN || || Anhalten (Clock läuft weiter!) | ||

|- | |- | ||

| | | Gate || GATE 1 - 16 || OUT || || Einzelausgang pro Step | ||

|- | |- | ||

| | | PW [[LFO]] || PULSE || OUT || || Rechteck | ||

|- | |- | ||

| | | PW LFO || RAMP || OUT || CLK FM || Sägezahn/Triangle | ||

|- | |- | ||

| | | PW LFO || SYNC IN || IN || || Zum Synchronisieren | ||

|- | |- | ||

| | | CV LFO || SQUARE || OUT || || 50% Rechteck | ||

| | |||

| | |||

|- | |- | ||

| | | CV LFO || TRIANGLE || OUT || || Dreieck | ||

|- | |- | ||

| | | CV LFO || SPEED CV || IN || ROW B || Geschwindigkeit | ||

|- | |- | ||

| | | Level || MIX IN || IN || ROW B | ||

|- | |- | ||

| | | Level || LEVEL OUT + || OUT | ||

|- | |- | ||

| | | Level || LEVEL OUT - || OUT | ||

|- | |- | ||

| | | Multi || 1 (über dem M) || IN || Clock | ||

|- | |- | ||

| | | Multi || 2-3 || OUT | ||

|- | |- | ||

| | | Slew || SLEW IN || IN || ROW A | ||

|- | |- | ||

| | | Slew || RESET || IN | ||

|- | |- | ||

| | | Slew || SLEW OUT || OUT | ||

|- | |- | ||

| | | [[S&H]] || S+H IN || IN || PW LFO | ||

|- | |- | ||

| | | S&H || TRIGGER || IN || Clock | ||

|- | |- | ||

| | | S&H || S+H OUT || OUT | ||

|- | |- | ||

| | | Trigger Delay || DELAY IN || IN || Clock | ||

|- | |- | ||

| | | Trigger Delay || DELAY OUT || OUT | ||

|- | |- | ||

|SEQ | | Length || SEQ TR OUT || OUT || || Rechteck LFO | ||

|- | |- | ||

| | | Length || SEQ LENGTH || IN || 16 || Trigger/Gate input für Sequenz-Ende | ||

|- | |- | ||

|ROW A || OUT | | Sequencer Out || ROW A || OUT | ||

|- | |- | ||

|ROW B || OUT | | Sequencer Out || ROW B || OUT || SPEED CV | ||

|} | |} | ||

Unterer Teil | '''Unterer Teil:''' | ||

{| class="wikitable" | {| class="wikitable" | ||

|- class="hintergrundfarbe5" | |- class="hintergrundfarbe5" | ||

! Buchse !! Art !! | ! Modul !! Buchse !! Art !! Pre-Patched !! Beschreibung | ||

|- | |- | ||

| | | [[Clock]] & [[Trigger]] || START || IN | ||

|- | |- | ||

| | | Clock & Trigger || START/STOP || IN | ||

|- | |- | ||

| | | Clock & Trigger || STEP || IN || || Next Step 1 | ||

|- | |- | ||

| | | Clock & Trigger || RESET || IN || || Zurück auf Step 1 | ||

|- | |- | ||

| | | Clock & Trigger || CL OUT || OUT || Divider In || Gate (1,2 oder 3) | ||

|- | |- | ||

| | | Clock & Trigger || QT CLK OUT || OUT || || Quantizer Gate | ||

|- | |- | ||

| | | Clock & Trigger || OUT BUS 1 || OUT || || Gate 1 | ||

|- | |- | ||

| | | Clock & Trigger || OUT BUS 2 || OUT || || Gate 2 | ||

|- | |- | ||

| | | Clock & Trigger || OUT BUS 3 || OUT || || Gate 3 | ||

|- | |- | ||

| | | Divider || IN || IN || CL OUT || Gate | ||

|- | |- | ||

| 1 | | Divider || 1.n || OUT || || Jeder 2/4/8/16/32/64/128. | ||

|- | |- | ||

| | | Multi 1 || 1 (Links vom M) || IN || Clock | ||

|- | |- | ||

| | | Multi 1 || 2-3 || OUT | ||

|- | |- | ||

| | | Multi 2 || 1 - 4 | ||

|- | |- | ||

| | | [[Quantizer]] || 1 QUA IN || IN || 1 CHA OUT || 1 Bei 1-16 und 1 Bei 2x8 | ||

|- | |- | ||

| | | Quantizer || 2 QUA IN || IN || 2 CHA OUT || (Bei 2x8) 2 Bei 2x8 | ||

|- | |- | ||

| | | Quantizer || CV 1 QUA IN || IN || || Add to QUA 1 | ||

|- | |- | ||

| | | Quantizer || 1 QUA OUT || OUT | ||

|- | |- | ||

| | | Quantizer || 2 QUA OUT || OUT | ||

|- | |- | ||

| | | CL P1 || FM CLK || IN || OUT BUS 1 || Geschwindigkeit | ||

|- | |- | ||

| | | CL P1 || CLK PWM || IN || || Gate Länge | ||

|- | |- | ||

| | | CL P1 || OUT POS 1 || OUT || || Gate bei STEP 1 | ||

|- | |- | ||

| | | Channel Outs || 1 CHA OUT || OUT || || CV 1-16 bzw. 1-8 Bei 2x8 | ||

|- | |- | ||

| | | Channel Outs || 2 CHA OUT || OUT || || CV 1-16 bzw. 9-16 Bei 2x8 | ||

|- | |- | ||

| 1 | | Inverter 1 || 1 INV IN || IN | ||

|- | |- | ||

| | | Inverter 1 || 1 INV OUT || OUT | ||

|- | |- | ||

| 2 INV IN || IN | | Inverter 2 || 2 INV IN || IN | ||

|- | |- | ||

| 2 INV OUT || OUT | | Inverter 2 || 2 INV OUT || OUT | ||

|- | |- | ||

| | | [[AND]]|| 1 AND IN || IN | ||

|- | |- | ||

| | | AND || 2 AND IN || IN | ||

|- | |- | ||

| | | AND || AND OUT || OUT | ||

|- | |- | ||

| | | [[OR]] || 1 OR IN || IN | ||

|- | |- | ||

| | | OR || 2 OR IN || IN | ||

|- | |- | ||

| | | OR || OR OUT || OUT | ||

|- | |- | ||

| | | XOR || 1 XOR IN || IN | ||

|- | |- | ||

| | | [[XOR]] || 2 XOR IN || IN | ||

|- | |- | ||

| | | XOR || XOR OUT || OUT | ||

| | |||

| XOR OUT || OUT | |||

|} | |} | ||

== Oberer Teil == | |||

=== Anzahl Schritte setzen === | |||

Entweder den [[Gate]]-Ausgang mit Reset-In verbinden oder mit dem Seq Length Eingang. Beim Reset-Eingang muss man allerdings das Folge-Gate benutzen (2 Schritte = Gate 3 mit Reset-In verbinden, statt Gate 2). | |||

=== Technische Daten === | |||

2. [[Sequencer]] Reihe oben geht bis 10 V. | |||

==== LFOs ==== | |||

Der CV LFO reicht von 1.4 bis 25Hz, der PW LFO bis max. 0.3 Hz. | |||

== Unterer Teil == | |||

Der untere Teil ist sehr stark am [[ARP]] [[Sequencer]] 1601 orientiert. | |||

== Bekannte Fehler == | |||

== | === Unterer Teil === | ||

==== Übersprechen der Gate-Bus-Schalter im 2x8 Modus ==== | |||

Die Gate-Bus-Schalter übersprechen im 2x8 Modus. Im 1x16 Modus tritt dies nicht auf! | |||

'''Schritte zur Reproduktion''' | |||

1. Alle Gate-Bus-Schalter auf Bus 2 stellen<br> | |||

2. Out Bus 1 mit dem Step-Eingang verbinden<br> | |||

3. Out Bus 3 mit dem Reset-Eingang verbinden (Skip/Reset/Norm auf Norm stellen)<br> | |||

4. Mode auf 2x8 stellen<br> | |||

5. Einen Gate-Bus-Schalter auf Bus 1 oder 3 schalten, während ein | |||

anderer Schritt läuft | |||

'''Ist-Zustand''' | |||

Der Sequencer springt direkt oder stellt sich direkt zurück. | |||

'''Soll-Zustand''' | |||

Der Sequencer soll erst am geänderten Schritt reagieren. | |||

'''Fix''' | |||

[http://www.sequencer.de/synthesizer/viewtopic.php?p=521490#p521490 Fix-Beschreibung von tomcat] | |||

Aktuelle Version vom 17. Februar 2013, 21:46 Uhr

Übersicht

Ein-/Ausgänge mit Pre-Patchings

Oberer Teil:

| Modul | Buchse | Art | Pre-Patch | Beschreibung |

|---|---|---|---|---|

| Clock | CLK FM | IN | RAMP | Clock Frequency |

| Clock | CLK PWM | IN | Länge des Gates | |

| Clock | EXT CLK | IN | Externe Clock | |

| Clock | RESET | IN | Zurück auf Gate 1 | |

| Clock | PULSE | OUT | Gate als Rechteck | |

| Clock | SQUARE | OUT | Gate als 50% Rechteck | |

| Clock | HOLD | IN | Anhalten (Clock läuft weiter!) | |

| Gate | GATE 1 - 16 | OUT | Einzelausgang pro Step | |

| PW LFO | PULSE | OUT | Rechteck | |

| PW LFO | RAMP | OUT | CLK FM | Sägezahn/Triangle |

| PW LFO | SYNC IN | IN | Zum Synchronisieren | |

| CV LFO | SQUARE | OUT | 50% Rechteck | |

| CV LFO | TRIANGLE | OUT | Dreieck | |

| CV LFO | SPEED CV | IN | ROW B | Geschwindigkeit |

| Level | MIX IN | IN | ROW B | |

| Level | LEVEL OUT + | OUT | ||

| Level | LEVEL OUT - | OUT | ||

| Multi | 1 (über dem M) | IN | Clock | |

| Multi | 2-3 | OUT | ||

| Slew | SLEW IN | IN | ROW A | |

| Slew | RESET | IN | ||

| Slew | SLEW OUT | OUT | ||

| S&H | S+H IN | IN | PW LFO | |

| S&H | TRIGGER | IN | Clock | |

| S&H | S+H OUT | OUT | ||

| Trigger Delay | DELAY IN | IN | Clock | |

| Trigger Delay | DELAY OUT | OUT | ||

| Length | SEQ TR OUT | OUT | Rechteck LFO | |

| Length | SEQ LENGTH | IN | 16 | Trigger/Gate input für Sequenz-Ende |

| Sequencer Out | ROW A | OUT | ||

| Sequencer Out | ROW B | OUT | SPEED CV |

Unterer Teil:

| Modul | Buchse | Art | Pre-Patched | Beschreibung |

|---|---|---|---|---|

| Clock & Trigger | START | IN | ||

| Clock & Trigger | START/STOP | IN | ||

| Clock & Trigger | STEP | IN | Next Step 1 | |

| Clock & Trigger | RESET | IN | Zurück auf Step 1 | |

| Clock & Trigger | CL OUT | OUT | Divider In | Gate (1,2 oder 3) |

| Clock & Trigger | QT CLK OUT | OUT | Quantizer Gate | |

| Clock & Trigger | OUT BUS 1 | OUT | Gate 1 | |

| Clock & Trigger | OUT BUS 2 | OUT | Gate 2 | |

| Clock & Trigger | OUT BUS 3 | OUT | Gate 3 | |

| Divider | IN | IN | CL OUT | Gate |

| Divider | 1.n | OUT | Jeder 2/4/8/16/32/64/128. | |

| Multi 1 | 1 (Links vom M) | IN | Clock | |

| Multi 1 | 2-3 | OUT | ||

| Multi 2 | 1 - 4 | |||

| Quantizer | 1 QUA IN | IN | 1 CHA OUT | 1 Bei 1-16 und 1 Bei 2x8 |

| Quantizer | 2 QUA IN | IN | 2 CHA OUT | (Bei 2x8) 2 Bei 2x8 |

| Quantizer | CV 1 QUA IN | IN | Add to QUA 1 | |

| Quantizer | 1 QUA OUT | OUT | ||

| Quantizer | 2 QUA OUT | OUT | ||

| CL P1 | FM CLK | IN | OUT BUS 1 | Geschwindigkeit |

| CL P1 | CLK PWM | IN | Gate Länge | |

| CL P1 | OUT POS 1 | OUT | Gate bei STEP 1 | |

| Channel Outs | 1 CHA OUT | OUT | CV 1-16 bzw. 1-8 Bei 2x8 | |

| Channel Outs | 2 CHA OUT | OUT | CV 1-16 bzw. 9-16 Bei 2x8 | |

| Inverter 1 | 1 INV IN | IN | ||

| Inverter 1 | 1 INV OUT | OUT | ||

| Inverter 2 | 2 INV IN | IN | ||

| Inverter 2 | 2 INV OUT | OUT | ||

| AND | 1 AND IN | IN | ||

| AND | 2 AND IN | IN | ||

| AND | AND OUT | OUT | ||

| OR | 1 OR IN | IN | ||

| OR | 2 OR IN | IN | ||

| OR | OR OUT | OUT | ||

| XOR | 1 XOR IN | IN | ||

| XOR | 2 XOR IN | IN | ||

| XOR | XOR OUT | OUT |

Oberer Teil

Anzahl Schritte setzen

Entweder den Gate-Ausgang mit Reset-In verbinden oder mit dem Seq Length Eingang. Beim Reset-Eingang muss man allerdings das Folge-Gate benutzen (2 Schritte = Gate 3 mit Reset-In verbinden, statt Gate 2).

Technische Daten

2. Sequencer Reihe oben geht bis 10 V.

LFOs

Der CV LFO reicht von 1.4 bis 25Hz, der PW LFO bis max. 0.3 Hz.

Unterer Teil

Der untere Teil ist sehr stark am ARP Sequencer 1601 orientiert.

Bekannte Fehler

Unterer Teil

Übersprechen der Gate-Bus-Schalter im 2x8 Modus

Die Gate-Bus-Schalter übersprechen im 2x8 Modus. Im 1x16 Modus tritt dies nicht auf!

Schritte zur Reproduktion

1. Alle Gate-Bus-Schalter auf Bus 2 stellen

2. Out Bus 1 mit dem Step-Eingang verbinden

3. Out Bus 3 mit dem Reset-Eingang verbinden (Skip/Reset/Norm auf Norm stellen)

4. Mode auf 2x8 stellen

5. Einen Gate-Bus-Schalter auf Bus 1 oder 3 schalten, während ein

anderer Schritt läuft

Ist-Zustand

Der Sequencer springt direkt oder stellt sich direkt zurück.

Soll-Zustand

Der Sequencer soll erst am geänderten Schritt reagieren.

Fix